Durée: 1H

Module: Architecture des Ordinateurs

## Test Architectures des Ordinateur

### **Exercice 1**

I/ Soit une architecture de Von Neumann munie d'une mémoire ayant les caractéristiques suivantes :

- L'adresse maximale hexadécimal pouvant être pris par un mot mémoire est « FFFFFF »

- La capacité mémoire est de 256 Méga bits

- 1/ Donner le schéma de cette architecture.

- 2/ Calculer la taille du bus d'adresse qui permet d'accéder à cette mémoire.

- 3/ Calculer la taille d'un mot mémoire.

- 4/ Proposer une architecture réduite pour cette mémoire (nombre de lignes d'adresses ; nombre de lignes de données ; taille du registre de mémoire d'adresse.....)

II/ Supposant d'on a augmenté la taille de cette mémoire et la mémoire est extensible jusqu'à 1 Giga bits.

- 1/ Calculer le nombre total des mots mémoire après l'extension de cette mémoire.

- 2/ Calculer le nombre de bits réservés à l'adressage (après extension)

#### Exercice 2

I/ Classez les mémoires suivantes par taille, par rapidité : CD-ROM, Registre d'Instruction, Disques durs, ROM, Cache L1, USB, Cache L2.

II/ Soit une mémoire cache ayant les caractéristiques suivantes :

- 64 mots par lignes (mots de 4 octets)

- Taille de 64 ko L1 et L2 sont inclusifs

- 8 associatifs.

- Remplacement LFU.

- Taille de bus d'adresse : 32bits

- 1/ Combien y-a-t-il de blocs associatifs dans cette mémoire cache.

- 2/ Si un bloc n'est pas présent en cache L1, combien de lignes de L1 aura-t-on parcouru ? III/ A partir des performances du tableau ci-dessous calculer le temps d'exécution moyen d'une instruction pour chaque niveau sachant que durée d'un cycle horloge est **T.**

| Niveau   | Temps d'accès<br>succès (ns) | Taux de succès<br>(ns) | Pénalité d'échec<br>(Cycles) | Taille |

|----------|------------------------------|------------------------|------------------------------|--------|

| Cache L1 | 3                            | 80%                    | 5                            | 128 Ko |

| Cache L2 | 5                            | 90%                    | 10                           | 512 Ko |

LMD-MI-S3 Année 2019/2020

Module: Architecture des Ordinateurs

# Corrigé Test Architectures des Ordinateur

## Exercice 1 (8,5 points)

I/ Soit une architecture de Von Neumann munie d'une mémoire ayant les caractéristiques suivantes :

- L'adresse maximale hexadécimal pouvant être pris par un mot mémoire est « FFFFFF »

- La capacité mémoire est de 256 Méga bits

- 1/ Donner le schéma de cette architecture. (2 points)

- 2/ Calculer la taille du bus d'adresse qui permet d'accéder à cette mémoire. (1 point)

3/ Calculer la taille d'un mot mémoire. (1,5 point)

Capacité= Nombre de mots \* taille du mot → taille du mot = Capacité/ Nombre de mots

Nombre de mots =  $2^{\text{nombre de lignes d'adresse}}$  sachant que nombre de lignes d'adresse= taille du bus

d'adresse (les formules sur 0.75)

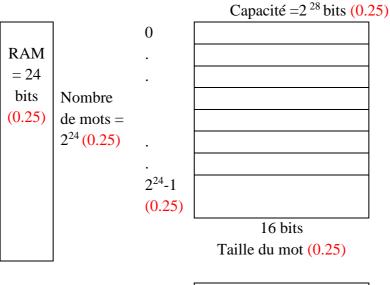

Donc Nombre de mots =  $2^{24}$  mots

Taille du mot = 256 M bits /  $2^{24} = 2^8 * 2^{20} / 2^{24} = 2^4$  bits (0.75)

4/ Proposer une architecture réduite pour cette mémoire (nombre de lignes d'adresses ; nombre de lignes de données ; taille du registre de mémoire d'adresse.....) (2 points)

Nombre de lignes d'adresses =24 = taille RAM Nombre de lignes de données =16 = taille RDM

(Dessin sur 0.5)

RDM =16 bits (0.25)

II/ Supposant d'on a augmenté la taille de cette mémoire et la mémoire est extensible jusqu'à 1 Giga bits.

1/ Calculer le nombre total des mots mémoire après l'extension de cette mémoire. (1 point)

Nombre de mots mémoire= Taille mémoire après l'extension/ taille du mot mémoire (0.5)

NMM=  $2^{30}/2^4 = 2^{26}$  mots (0.5)

2/ Calculer le nombre de bits réservés à l'adressage (après extension) (1 point)

LMD-MI-S3 Année 2019/2020

Module: Architecture des Ordinateurs

Nombre de mots =  $2^{\text{nombre de lignes d'adresse}}$  (0.5) =  $2^{26} \rightarrow 26$  bits d'adressage (0.5)

## Exercice 2 (6,5 points)

I/ Classez les mémoires suivantes par taille, par rapidité : CD-ROM, Registre d'Instruction, Disques durs, ROM, Cache L1, USB, Cache L2. (2 points)

Par taille : RI < L1 < L2 < ROM < CD < USB < DD. (1 point est -0.25 pour chaque erreur) Par vitesse : RI > L1 > L2 > ROM > DD > USB > CD. (1 point est -0.25 pour chaque erreur)

II/ Soit une mémoire cache ayant les caractéristiques suivantes :

- 64 mots par lignes (mots de 4 octets)

- Taille de 64 ko L1 et L2 sont inclusifs

- 8 associatifs.

- Remplacement LFU.

- Taille de bus d'adresse : 32bits

1/ Combien y-a-t-il de blocs associatifs dans cette mémoire cache (2 points)

Nombre de lignes = Taille cache /(Taille mot\* nombre de mots par ligne) (0.5)

$$= 64 \text{ KOct} / (4 \text{ Oct} * 64) = 2^{10}/2^2 = 256 (0.5)$$

Nombre de blocs = Nombre de lignes/ Nombre de lignes par bloc (0.5)

$$= 256/8 = 2^8/2^3 = 2^5 = 32 (0.5)$$

2/ Si un bloc n'est pas présent en cache L1, combien de lignes de L1 aura-t-on parcouru ? (0,5 point) 8 lignes

III/ A partir des performances du tableau ci-dessous calculer le temps d'exécution moyen d'une instruction pour chaque niveau sachant que durée d'un cycle horloge est **T. (2 points)**

| Niveau   | Temps d'accès | Taux de | Pénalité d'échec | Taille |

|----------|---------------|---------|------------------|--------|

|          | succès (ns)   | succès  | (Cycles)         |        |

| Cache L1 | 3             | 80%     | 5                | 128 Ko |

| Cache L2 | 5             | 90%     | 10               | 512 Ko |

temps d'accès mémoire moyen = temps d'accès succès + taux d'échec x pénalité d'échec (1) taux d'échec = 1 - taux de succès

temps d'accès mémoire moyen Cache L1 = 3 + (1-80%)x5 = 4T (0.5)

temps d'accès mémoire moyen Cache L2 = 5 + (1-90%)x10 = 6T (0.5)